|

[실전 강의실 VHDL]

|

|

하드웨어 설계, 이제는 프로그래밍으로! 2

완벽한 하드웨어 기술 언어, VHDL

지난 호에서 하드웨어를 디자인하는 다양한 방법에 대해 살펴봤다. 특히 주문형 반도체를 이용한 구현 방법 중에서도 반주문형 방식의 프로그래밍 가능한 소자를 이용한 구현 방법에 대해 보다 자세히 알아봤다. 이제 본격적으로 하드웨어 기술 언어를 이용한 디지털 시스템의 구현 방법을 알아 볼 차례다. 이번 호에서는 대표적인 하드웨어 기술 언어라 할 수 있는 VHDL의 문법과 프로그래밍 방법을 설명하고, 간단한 예제를 통해 그 사용법을 익혀보자.

|

연재순서

|

|

|

|

|

1회 2002.8 | 최상의 하드웨어 설계 방법을 찾아라

|

|

2회 2002.9 | 완벽한 하드웨어 기술언어, VHDL

|

|

3회 | 나의 첫 하드웨어 프로그래밍, 자판기 설계 프로젝트

|

|

|

|

연재가이드

|

|

|

|

|

운영체제 | 윈도우 98 이상

|

|

개발도구 | Xilinx Foundation (PC & UNIX)

|

|

기본지식 | 논리 회로, 디지털 시스템

|

|

응용분야 | 디지털 회로의 설계, ASIC/FPGA의 설계

|

|

|

|

|

|

곽종욱 celot@naver.com

|

|

|

|

하드웨어를 디자인할 수 있는 언어 VHDL과 Verilog 프로그래밍에 관심을 갖고 있으며, 링 기반 고성능 대형 컴퓨터 개발 프로젝트에 참여한 바 있다. 자신을 하드웨어 엔지니어라고 소개하는 필자는 이 글을 통해 디지털 시스템 설계와 하드웨어 기술 언어를 이용한 프로그래밍에 관심을 갖는 독자가 많아지기를 바란다고.

|

우리는 지난 호에서 하드웨어 기술 언어가 무엇이며, 이를 어떤 용도에 어떤 방식으로 사용하는가에 대해 설명했다. 이제 좀더 자세히 알아 볼 차례로 이번 호에서는 하드웨어 기술 언어로서의 VHDL에 대한 문법과 기본적인 사용 방법, 그리고 실제 프로그래밍할 때 필요한 VHDL의 다양한 표현 방법에 대해 살펴본다.

VHDL의 세계

VHDL은 기본적으로 ASIC과 같은 대규모 집적 회로의 설계시 주로 사용되는 언어로서, 기존의 하드웨어 설계시 필요한 회로도 입력의 번거로움을 대신해 단순히 코딩 형태의 텍스트를 입력함으로써 하드웨어의 동작을 묘사할 수 있게끔 설계된 하드웨어적 측면의 프로그래밍 언어라 할 수 있다. 이러한 VHDL은 회로의 연결 정보를 포함 할 뿐만 아니라 기존의 C 언어와 같은 프로그래밍 언어로서의 성격도 가지고 있어 매우 다양한 하드웨어 기술 방법을 제공한다. 또한 프로그래밍 언어의 외향만 따지자면 소프트웨어 프로그래머들에게는 가장 친숙하다고 할 수 있는 C 언어와 유사한 형태를 나타낸다. 차이가 있다면 C 언어는 소프트웨어의 특성상 모든 문장이 순차 구문으로만 구성된 반면 VHDL은 순차 구문 이외에 병렬 구문과 하드웨어 특유의 시간(timing) 개념이 있다는 것이다. 이는 비단 VHDL만의 특성이라 할 수 없으며 일반 하드웨어 기술 언어는 모두 이와 같은 기본적인 특징을 가지고 있다. 그럼 VHDL의 특징에 대해 자세히 살펴보자.

- 하드웨어 기술 언어로서의 표준화된 형태 제공 : 기존의 여러 하드웨어 기술 언어들이 존재하는 가운데 회사마다 각각 다르게 설계하던 다양성을 표준화된 VHDL이 등장함으로써 자료 교환, 보관, 문서화 등을 통일할 수 있게 되었다.

- 특정 프로세스 기술에 의존하지 않는 기술 독립적 형태를 제공 : 특정 설계 기술이나 제조 공정과는 무관하게 제품을 설계할 수 있다.

- 상위 레벨 언어 형태의 제공 : VHDL은 고급 프로그래밍 언어(HLL, High Level Language)와 같은 원리에 바탕을 두면서 하드웨어적 특징을 부가하여 표현 능력을 확장시켰다.

- 광범위한 설계 범위의 지원 : 간단한 하드웨어 모듈의 구현에서 뿐만 아니라 VLSI 수준의 고밀도 집적 회로의 설계시에도 용이하게 사용된다.

- 하향식(Top-Down) 설계 방법의 지원 : 하향식 형태의 설계 방식을 지원해 보다 복잡한 회로에 대한 설계 기간을 줄이고, 설계 과정에서 발생하기 쉬운 오류에 대한 수정 작업을 쉽게 해준다.

- 여러 가지의 설계 기법의 구현 : 대규모의 디지털 시스템에 대한 명세의 기술, 설계, 시뮬레이션 등의 프로그램이 가능해서 여러 가지 설계 기법을 적용할 수 있다. 즉 계층적 설계의 지원, 동기식/비동기식 설계 등이 가능하다.

- 폭 넓은 기술 범위 : 시스템 레벨에서부터 논리회로 레벨까지 하나의 언어로서 모두 기술이 가능하다.

- 복수 설계 그룹에 의한 공동 개발 가능 : 공동 라이브러리의 구축, 계층적 설계등을 이용하므로 다수의 그룹이 포함된 공동의 개발이 가능하다.

하지만 이와 같은 특징에도 불구하고 VHDL의 문제점도 있다. 하지만 다음에 살펴볼 문제점 또한 VHDL 내적인 요인이기보다는 설계자나 설계환경과 연관된 외적 요인이 많다. VHDL의 사용상의 난점이라면 다음과 같은 것들을 들 수 있다.

- 문법의 복잡성 : VHDL은 비교적 복잡한 언어이다. 이는 소프트웨어 언어적 관점에서 보면 큰 문제는 안 되지만 기존의 하드웨어 제작자의 입장에서는 새로운 언어를 익히는 것이 꽤 번거로운 일이 될 수 있다.

- 급격한 설계 방식의 변화 요구 : 기존의 상향식(Bottom-Up) 설계에 익숙한 제작자에게는 급작스런 설계 방식의 변화에 무리가 따를 수 있다. 이는 새로운 설계 환경의 도입이 필요함을 의미하며, 또한 설계 방법의 교육과 같은 이차적 비용이 추가적으로 발생할 수 있음을 뜻한다.

- 최적화 도구의 지원 필요 : VHDL은 하드웨어를 기술해 이를 시뮬레이션하기 위해 만들어진 언어이므로 설계자들의 또 다른 관심사라 할 수 있는 정확한 타이밍의 예측 및 임계 경로 등의 계산이 어렵다는 문제점이 있다. 다시 말해 VHDL은 하나의 언어로서의 가치가 있을 뿐 정작 그 언어가 사용될 환경이 충분히 지원되지 않는다면 빛 좋은 개살구에 불과하다는 것이다. 설계에 필요한 합성 도구와 최적화 도구의 지속적 지원이 필요하다는 뜻이다.

- 비효율적 회로의 생성 가능성 : VHDL로 설계한 후, CAD 툴이 합성한 논리회로는 사람이 직접 설계한 게이트 레벨의 회로보다 그 규모면에서 큰 경우가 종종 발생한다. 이 역시 최적화 도구의 지속적인 발전과 지원이 필요한 부분이다.

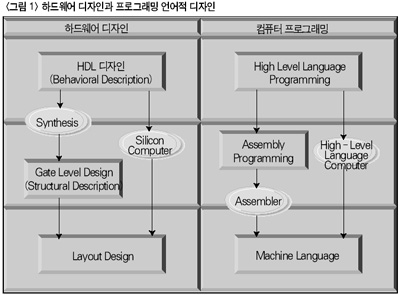

<그림 1>은 VHDL을 이용한 설계와 기존의 프로그래밍 언어를 이용한 소프트웨어 제작에 있어 설계상의 차이점과 유사점을 나타내는 것이다. VHDL을 이용한 하드웨어 디자인도 일반 소프트웨어 언어적인 특징을 가지고 있어 그 처리 과정이 소프트웨어의 그것과 비교해 볼 때 컴퓨터 프로그래밍과 용어적인 차이가 있을뿐 설계상의 절차를 비교하면 크게 차이나지 않는다.

일단 절차적 설계 방식으로 작성한 VHDL 코드는 소프트웨어 적 측면에서 볼 때 프로그래밍 이후 컴파일 과정을 거치듯이 하드웨어적인 전처리 합성(pre-synthesis) 과정을 거친다. 이렇게 해서 생긴 결과물은 게이트와 RTL 레벨의 구조적 형태의 코드이다. 이 부분은 컴퓨터 프로그래밍 부분의 어셈블리 프로그래밍에 해당되는 부분이라 할 수 있을 것이다. 그리고 이를 어셈블러를 통해 실제 하드웨어가 인식할 수 있는 기계어로 바꿔준다. 이에 대응하는 VHDL을 이용한 하드웨어 디자인에서는 이러한 게이트 레벨의 코드를 본 합성 과정을 거처 네트리스트(netlist)로 결과물을 만들고 이를 이용해 레이아웃에서 실제 구현 작업을 수행한다.

한 가지 부연하자면 VHDL에서는 처음 초기의 코딩 단계로서 절차적 명세(behavioral description)에 의한 프로그래밍을 수행하고 이를 다시 게이트와 RTL 레벨의 구조적 명세(structural description)에 의한 프로그래밍으로 변환했지만, 사실 VHDL을 이용해 직접 처음부터 구조적 명세에 의한 게이트와 RTL 레벨의 프로그래밍을 할 수 있다. 이는 소프트웨어적 측면에서 볼 때 C/C++와 같은 상위 언어를 이용하지 않고 일반 80×86 시리즈의 어셈블리 언어를 직접 사용해 프로그래밍하는 것과 같이 서로 비교해 설명될 수 있다. 이 또한 하드웨어와 소프트웨어 분야의 프로그래밍 방식의 유사성을 보여주는 좋은 예라 할 수 있을 것이다. 지금까지 우리는 VHDL이 가지는 장점과 나름대로의 문제점, 그리고 소프트웨어의 그것과 비교했을 때의 차이점과 유사점에 대해 알아봤다. 이와 같은 기본적인 VHDL의 특징을 이해했으리라 보고, 이제 다음으로 하나의 언어로서의 VHDL에 대해서 본격적으로 알아보자.

언어로서의 VHDL

지금부터 언어로서의 VHDL을 살펴보자. 즉, 실제 VHDL을 사용하는 데 필요한 기본적인 사항을 사용 방법과 주의 사항 위주로 알아보기로 한다. 먼저 VHDL에서 사용하는 식별어(identifier), 예약어(reserved word), 그리고 주석(comment)에 대해 알아보자. 이제 설명할 세 가지 용어는 일반 소프트웨어 프로그래밍에서도 형태와 상황은 다르지만 같은 의미를 가진다. 참고로 VHDL에서는 알파벳의 대소문자를 구분하지 않는다.

식별어

식별어는 일반 프로그래밍 언어에서와 마찬가지 의미를 지닌다. VHDL에서는 엔터티(entity) 이름, 아키텍처 몸체(architecture body), 포트(port) 그리고 함수(function) 등을 정의하기 위해 사용된다. 이제 막 나열한 구체적인 용어에 대해서는 본 연재의 뒷 부분에서 하나씩 알아 볼 것이다. 일반 프로그래밍 언어의 그것과 마찬가지로 VHDL도 식별어의 첫 번째 문자는 반드시 영문으로 시작하며 두 번째 문자부터 영문자 및 숫자 그리고 언더바(_)등이 올 수 있다.

예약어 또는 키워드

예약어는 VHDL 구문에서 미리 그 의미가 지정되어 있는 문자열로서 예약어는 식별어로 사용할 수 없다. 보통 사용자는 프로그램 편집기에서 이러한 예약어와 식별어를 구분하기 위해 식별어는 대문자로, 예약어는 소문자로 사용하는 방식의 나름대로의 통일성을 가지고 프로그래밍하기도 하고 특히 CPLD나 FPGA 제조회사에서 제공하는 문서 편집기를 이용할 경우 시각적으로 서로 다른 색깔을 사용함으로써 이를 구분해 주는 경우도 있다. <표 1>에 예약어가 알파벳 순서로 정렬되어 있다.

<표 1> VHDL의 예약어

|

abs

|

access

|

after

|

alias

|

all

|

and

|

|

architecture

|

array

|

assert

|

attribute

|

|

|

|

begin

|

block

|

body

|

buffer

|

bus

|

|

|

case

|

component

|

configuration

|

constant

|

|

|

|

disconnect

|

|

downto

|

|

|

|

|

else

|

elsif

|

end

|

entity

|

exit

|

|

|

file

|

for

|

function

|

|

|

|

|

generate

|

generic

|

guarded

|

|

|

|

|

if

|

in

|

inout

|

is

|

|

|

|

label

|

library

|

linkage

|

loop

|

|

|

|

map

|

mod

|

|

|

|

|

|

nand

|

new

|

nor

|

not

|

null

|

|

|

of

|

on

|

open

|

or

|

others

|

out

|

|

package

|

port

|

procedure

|

|

process

|

|

|

range

|

record

|

register

|

rem

|

report

|

return

|

|

select

|

severity

|

signal

|

|

subtype

|

|

|

then

|

to

|

transport

|

type

|

|

|

|

unit

|

until

|

use

|

|

|

|

|

variable

|

|

|

|

|

|

|

wait

|

when

|

while

|

|

with

|

|

|

xor

|

|

|

|

|

|

주석

VHDL에서 주석은 - - 로 표시된다. 여느 프로그래밍 언어에서와 마찬가지로 이러한 주석문은 VHDL의 수행에는 아무런 영향을 미치지 않는다. 프로그래밍에서의 습관이라고 할 수 있겠으나 프로그래머나 설계자에 따라서 주석을 활용하는 부류와 그렇지 않는 부류의 사람들이 확연히 구분되어지는 경우가 종종 있다. 올바른 프로그래밍 습관은 가급적 주석문을 많이 활용해 이를 문서에 포함토록 하는 것이다. 이는 프로그래밍의 양이 방대해지고 또 개발 기간이 길어짐에 따라 문서화에도 도움이 돼 프로그래밍할 때 이점으로 작용한다.

기타 VHDL을 사용할 때는 다음과 같은 주의 사항들이 있다.

- 모든 알파벳은 대문자와 소문자를 구별하지 않고 똑같이 취급한다. 따라서 변수 선언이나 사용시에 이에 대한 혼란이 없도록 한다.

- 주석은 마이너스(-) 두 개로 시작하며, 그 줄 끝까지만 유효하다.

- 한 문장은 세미콜론(;)으로 끝나야 한다.

- 식별어가 한 라인을 넘길 수 없다.

- 식별어 중간에 공백을 사용할 수 없으며, 여러 개의 식별어 나열시에는 콤마(,)로서 구분한다.

- 식별어의 처음 부분에 언더바(_)를 사용할 수 없으며, 연속된 두 개의 언더바, 마지막 문자로의 언더바를 사용할 수 없다.

VHDL의 기본 구성

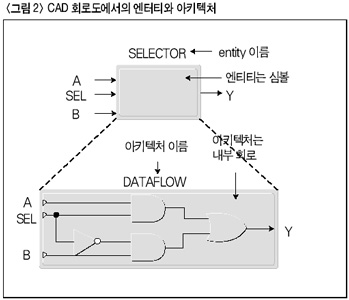

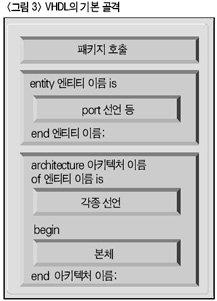

보통 CAD 툴을 이용해 회로를 설계할 때는 <그림 2>와 같이 몇몇 심볼들을 사용해 제작한다. 이러한 CAD로 디자인한 회로도에서 볼 때 심볼에 해당하는 부분, 즉 입출력의 설계에 해당하는 부분이 VHDL에서는 엔터티를 선언하는 부분이 된다. 그리고 이러한 엔터티의 내부 설계, 즉 심볼의 내부 회로도에 해당하는 부분이 아키텍처 몸체에 해당하며 이 몸체 내부에서 실제 그 모듈의 구현이 이뤄진다. 이와 같이 VHDL은 그 기본 골격으로 엔터티와 아키텍처 몸체를 가진다. 보다 더 직관적인 블럭 형태로 이를 도식화한 것이 <그림 3>이다.

이러한 <그림 3>과 같은 기본 골격을 보다 더 자세히 이해하기 위해 간단한 형태의 VHDL 코드가 다음과 같이 제시돼 있다. 우리가 살펴볼 첫 번째 VHDL 코드이다. 이 코드는 <그림 2>에 해당하는 회로를 묘사한 코드이다. 코딩 방법적 측면에서의 설명은 차차 이야기할 것이며 우선 그 골격을 눈여겨보기 바란다.

-- <그림 2>를 VHDL로 묘사한 코드

library ieee;

use ieee.std_logic_1164.all; -- 이상 사용할 라이브러리의 선언

entity SELECTOR is -- SELECTOR는 엔터티의 이름

port( A,B : in std_logic; -- 사용할 핀들의 정의

SEL : in std_logic;

Y : out std_logic );

end SELECTOR;

architecture DATAFLOW of SELECTOR is --DATAFLOW는 아키텍처 이름

begin

Y <= (SEL and A) or (not SEL and B); -- 구현하고자 하는 기능

-- 의 논리식

end DATAFLOW;

첫 번째 VHDL 예제이니 만큼 소스 코드에 대해 간단히 알아보자. 우선 library라는 예약어가 있다. 이는 C 프로그래밍의 include문과 비슷한 것으로 본 예제에서는 ieee에 해당하는 라이브러리를 코드 내에 불러와 사용하겠다는 의미이다. 즉 라이브러리를 선언하는 부분이다. 그 다음에 나와 있는 use 문장은 이 라이브러리의 사용 범위를 설명하는 문장이다. 즉 해당 라이브러리의 무엇을 가져와 사용할지를 나타낸다. 이러한 엔터티 앞에 쓰여진 library의 선언은 하나의 엔터티 선언, 혹은 그에 부속되어 있는 아키텍처, 구성(configuration)까지 영향을 미친다. 또한 use문은 하나의 파일 내에 두 개 이상의 엔터티 선언이 있는 경우에도 필요하다.

다시 코드로 돌아가자. 그 다음으로 나와 있는 것이 바로 엔터티이다. 여기서는 SELECTOR라는 엔터티를 선언하고 있다. 즉 SELECOTR가 엔터티의 이름인 것이다. 그리고 그 엔터티 내부에는 A, B, SEL, Y라는 포트들이 존재한다. 그리고 비로소 아키텍처 내부에 이 SELECTOR라는 엔터티 모듈이 수행하는 동작이 묘사되어 있다. 즉 코드 내부의 구현하고자 하는 기능의 논리식이 여기에 해당된다.

지금까지 우리는 VHDL의 첫 번째 예제로서 <그림 2>를 VHDL로 구현한 코드를 알아봤다. 아직까지는 대충 이런 거구나 정도로만 이해하고 넘어가도 무난하다. 지금부터 하나씩 VHDL의 세부 요소에 대해서 설명할 것이다. VHDL을 이용해 하드웨어적으로 표현하기 위해서는 앞서 설명한 엔터티와 아키텍처 이외에 몇 가지의 구성 요소가 더 있다. 엔터티와 아키텍처 이외에 것을 함께 비교해 나가면서 살펴보자.

엔터티 선언 단위

앞서 설명했듯이 엔터티 선언(entity declaration)은 설계 회로의 입출력과 모듈의 외부 인터페이스를 정의한다. 하나의 회로에는 하나의 엔터티 선언만이 존재하는 반면에 표현하는 방법에 따라서 여러 개의 아키텍처 몸체가 존재할 수 있다. 지난 연재에서 설명했듯이 기본적으로 몸체 내부에서는 절차적 모델링과 구조적 모델링이 가능하며 그리고 이번 호에서 소개할 자료 흐름적 모델링도 할 수 있다. 각각의 모델링 기법에 대한 예제는 뒤에서 살펴 보기로 한다.

-- 엔터티 선언문의 형식

entity 엔터티_이름 is

[generic (범용문_표시자);]

[port (포트_리스트);]

{선언문}

{ begin(문장) }

end [엔터티_이름];

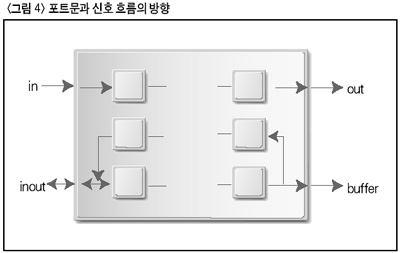

엔터티의 입출력을 정의함에 있어 VHDL에서 사용할 수 있는 신호의 종류는 총 다섯 가지가 있다. <그림 4>에서와 같이 나타난 신호의 흐름은 다음과 같다.

- in : 신호가 해당 엔터티로 입력되는 경우에 사용된다.

- out : 해당 엔터티에서 신호가 출력되는 경우에 사용된다.

- inout : 신호가 해당 엔터티로 들어가고 나가는 경우에 사용한다. 즉 양방향성 포트에 사용된다. 이 때 다수 개의 소스로부터의 업데이트가 가능하다.

- buffer : 출력 기능에서 신호를 엔터티 내에서 다시 읽는 기능을 추가한 것이다. 즉 출력을 내부에서 다시 사용할 수 있도록 한 것이다. 이때 업데이트 시키는 소스는 하나로 제한된다.

- linkage : 단순히 연결만 되어 있는 상태이다. 위의 어느 경우에도 해당되지 않고 단지 포트로만 연결되어 있는 경우이다.

아키텍처 몸체 단위

아키텍처 몸체는 하드웨어 내부와 내부 회로들의 연결·동작·구조 등을 표현한다. 그리고 이 아키텍처 내에는 하드웨어 특유의 병행문이 포함된다. 이는 하드웨어적 특징이라 할 수 있다. 즉 아키텍처 몸체 내에서 프로그래밍된 병행문은 하드웨어상의 네트리스트와 같은 의미로서 수행되기 때문에 코드 내의 위치상 선후 관계와 실행 순서와는 실제 아무런 상관이 없다. 소프트웨어 프로그래밍과의 중요한 차이점이라 하겠다. 이외에도 VHDL은 하드웨어 기술 언어임에도 불구하고 일반 언어에서와 마찬가지로 순차문을 지원하고 있다. 이러한 순차문은 프로세스문 내에서만 기술될 수 있다.

-- 아키텍처 몸체의 구성 형식

architecture 아키텍처_이름 of 엔터티_이름 is

{선언문}

begin

문장 내부의 동작적 표현;

end [아키텍처_이름];

패키지 선언 단위와 몸체 단위

VHDL에서 자료형과 부 프로그램 등을 하나의 파일로 만드는 것을 패키지라고 한다. 이러한 패키지는 자료형과 함수, 프로시저등을 중복으로 선언하거나 기술하지 않고 한번만 기술하여 이를 여러 설계에서 공동으로 사용토록 모아 둔 것을 의미한다. 일반 프로그래밍 언어의 라이브러리 및 헤더 파일과 같은 개념이라고 해도 될 것이다. 이러한 패키지도 엔터티와 아키텍처처럼 각각 선언과 몸체의 단위로 구분된다.

패키지 선언(package declaration)에서는 외부에서 필요한 데이터 타입이나 부 프로그램 등을 선언하는 것이고, 몸체는 패키지 선언 부분에서 정의한 부 프로그램의 구현을 담당하는 부분이다.

-- 패키지 선언

package 패키지_이름 is

{선언문}

end 패키지_이름

-- 패키지 몸체

package body 패키지_이름 is

{구현 문장}

end 패키지_이름;

구성 선언 단위

끝으로 알아볼 단위는 구성 선언(configuration declaration) 단위이다. 구성 선언 단위에서는 기본적으로 엔터티와 아키텍처 간에 상호 연결을 표현한다. 보통 하나의 엔터티는 여러 개의 아키텍처를 가질 수 있으며, 각각의 아키텍처는 여러 형태의 동작 표현으로 구성될 수 있다. 이런 동작의 특성을 따로 표현하거나 현재의 파일에서 사용한 동작의 표현을 기술할 수 있게 만든 것이 구성이다. 이러한 구성 선언은 설계한 회로의 상태를 간단히 설명해 주며, 이 특성을 이용해 계층 구조 형식의 하향식 설계 회로를 시뮬레이션이나 합성시 이미 별도로 합성된 다른 파일과 연결시켜 주는 역할도 한다. 링커(linker)와 비슷한 역할이라 할 것이다.

-- 구성 선언 형식

configuration 구성_이름 of 엔터티_이름 is

[use 관련문 | Attribute 지정]

block_configuration

end [configuration] [구성_이름];

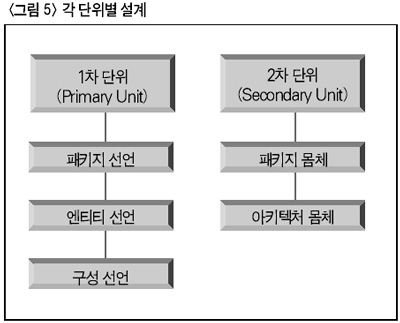

지금까지 우리는 VHDL의 기본 구성에 대해 살펴봤다. 첫 예제를 통해 VHDL 프로그래밍의 맛보기를 했으며, 이를 바탕으로 VHDL의 기본적인 설계 단위까지 알아봤다. 이상에서 설명한 각각의 설계의 단위를 전체적인 관점에서 보면 <그림 5>와 같이 나타낼 수 있다. 즉 설계의 단위를 1차 단위와 2차 단위로 크게 구분했을 경우, 1차 설계 단위로 패키지와 엔터티 그리고 구성 부분의 선언을 해 준다. 그리고 각각의 선언 단위에 해당하는 부분을 2차 단위인 몸체 부분에서 구현해 나가게 된다.

객체와 연산자

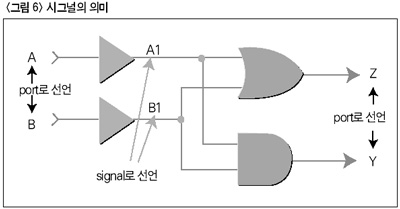

설계의 각 단위를 알아봤으니 이제 다음으로 VHDL에서 제공하는 객체(object)와 연산자(operator)에 대해 알아보도록 하자. 객체는 주어진 특정 자료형(data type)의 값을 가질 수 있는 대상이 되는 것으로서, VHDL에서는 크게 시그널(signal), 상수(constant), 변수(variable)의 3가지 종류의 객체가 있다. 각각은 서로 다른 특징을 나타내므로 잘 구분해 사용해야 한다. 시그널은 우선 포트와 비교해 이해해야 한다(<그림 6>). 포트와 시그널은 그 기준이 내부 신호인가 외부 신호인가에 따라 구분된다. 즉 모듈 외부에서 사용할 경우는 포트로 선언해야 하며 내부에서만 사용될 경우는 시그널로 선언해야 한다. 이 밖에 시그널은 변수/상수와 비교했을 때 시간의 개념이 있다는 것도 중요한 특징이다.

그 외에 변수와 상수는 일반 프로그래밍 언어의 그것과 동일하다. 상수는 한 번 정의되면 시뮬레이션 도중의 그 객체의 값에 변경을 불허하는 객체이다. 이에 반해 변수는 값의 계산과 동시에 그 값이 변경되는 객체를 의미한다. '값이 변한다'는 것과 '동시'에라는 것이 변수의 중요 특징이다. 왜냐하면 변수와 비교해서 시그널은 값이 변하기는 하되 하드웨어의 특성상 일정한 전파 지연(propagation delay) 시간의 값을 가진 후에 그 값이 변하기 때문이고 변수는 이러한 지연 시간에 대한 개념이 없다는 것이다. 지금까지의 설명이 <표 2>에 요약돼 있다.

<표 2> VHDL의 객체형과 그 특징

|

객체형

|

의미

|

변경 가능

|

시간 개념

|

선언할 수 있는 장소

|

|

signal

|

신호의 선언

|

가능

|

있슴

|

architecture, package, entity

|

|

variable

|

변수의 선언

|

가능

|

없슴

|

process, function, procedure

|

|

constant

|

상수의 선언

|

불가능

|

없슴

|

architecture, package, entity, process, function, procedure

|

이제 다음으로 VHDL에서 제공하는 연산자에 대해 알아보자. 연산자는 <표 3>에서 보는 바와 같이 크게 논리 연산자, 산술 연산자, 관계 연산자로 나뉜다. 그 외에 특수 연산자로서 연결 연산자, 부호 연산자, 기타 연산자 등이 있다. 이러한 연산자들 사이에는 그들 간의 우선순위가 존재한다. 역시 일반 프로그래밍 언어와 유사한 개념이라 할 수 있다. <표 3>에서는 논리 연산자가 가장 우선 순위가 높다는 것을 의미한다.

<표 3> VHDL의 연산자

|

구분

|

|

종류

|

우선순위

|

|

논리 연산자

(logical operator)

|

and

|

Logical AND

|

6

|

|

or

|

Logical OR

|

|

nand

|

Logical NAND

|

|

nor

|

Logical NOR

|

|

xor

|

Logical Exclusive OR

|

|

관계 연산자

(relational operator)

|

=

|

Equal

|

5

|

|

/=

|

Not Equal

|

|

<

|

Less Than

|

|

<=

|

Less Than or Equal

|

|

>

|

Greater Than

|

|

>=

|

Greater Than or Equal

|

|

연결 연산자

(concatenation operator)

|

&

|

Concatenation

|

4

|

|

산술 연산자

(arithmetic operator)

|

+

|

Addition

|

|

-

|

Subtraction

|

|

부호 연산자

(sign operator)

|

+

|

Unary Plus

|

3

|

|

-

|

Unary minus

|

|

*

|

multiplication

|

|

산술 연산자

(arithmetic operator)

|

/

|

Division

|

2

|

|

mod

|

Modulus

|

|

rem

|

Remainder

|

|

기타 연산자

|

**

|

Exponentiation

|

1

|

|

abs

|

Absolute Value

|

|

not

|

Complement

|

이 밖에도 VHDL에서는 4개의 시프트(shift) 연산자와 2개의 회전(rotate) 연산자를 제공한다. SLL(Shift Left Logical)/SRL(Shift Right Logical)/SLA(Shift Left Arithmetic)/SRA(Shift Right Arithmetic)가 4가지 시프트 연산자에 해당한다. 이때 논리 시프트와 산술 시프트의 차이는 이동 연산으로 인해 잘려 나가는(truncate) 비트 반대쪽의 새로 생기는 부분에 무슨 값을 채워 넣느냐에 따라 구분된다. 이때 0을 채워 넣는 경우 논리 시프트 연산에 해당되며, 새로 생긴 그 이전 자리의 값을 그대로 채워 넣으면 산술 시프트에 해당한다. 그 외 ROL(Rotate Left Logical)/ROR(Rotate Right Logical)의 2가지 회전 연산자가 있다.

동시 처리문과 순차 처리문

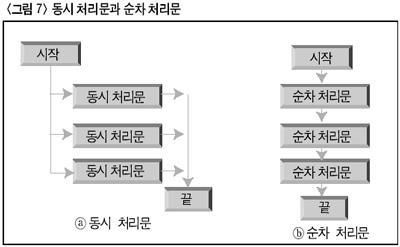

VHDL은 기본적으로 하드웨어를 기술하기 위한 언어이다. 이러한 하드웨어 기술 언어가 가지는 가장 큰 특징 중 하나가 동시 처리문이다. 이는 일반 프로그래밍 언어에서만 존재하는 순차 처리문과는 상당한 차이가 있는 처리 방식이다. 일반 프로그래밍 언어에서는 특정 블럭, 가령 'begin ~ end'사이에 있는 문장들이 <그림 7>의 ⓑ에서 보는 바와 같이 각각 순차적으로 수행된다. 이는 어쩌면 당연한 일인지도 모른다. 하지만 동시 처리문은 <그림 7>의 ⓐ에서 보는 바와 같이 모든 문장들이 동시에 처리된다. VHDL에서의 대표적 동시 처리문으로 'with select'문과 'when else'문이 있다.

순차 처리문은 인간의 사고방식과 유사한 특징이 있다. 그래서 어쩌면 동시 처리문을 지원하는 하드웨어의 프로그래밍이 어려운 것인지도 모르겠다. 그리고 이는 하드웨어 관련 프로그래밍 작업을 수행할 경우 막연히 회로의 동작에 대한 논리적 묘사만으로는 우리가 원하는 적절한 하드웨어의 구현을 보장하지 못한다는 의미가 된다. 하드웨어의 각 모듈들은 일반적으로 클럭에 동기화되어 있다. 그리고 그 클럭의 동작에 맞춰 각 모듈이 필요할 경우 각각 적절한 행동을 취한다. 이 경우 각 모듈들은 동시에 행동을 취하게 되는 것이다. 즉 각각의 모듈들이 병렬적으로 동작한다는 의미이다. 그리고 이는 각 모듈뿐만이 아니라 모듈 내부에서도 얼마든지 병렬적으로 수행할 가능성이 있음을 나타낸다.

순차 처리문은 앞서 설명했듯이 문장이 나열된 순서대로 처리되며 순차 처리문의 처음에는 반드시‘process’문을 사용해야 한다. 또한 순차 처리문에는 Sensitivity List라는 것이 포함돼 있다. 번역하면 신호 감지 목록이라는 표현이 적절할 것이다. 이는 순차 처리문에서 수행을 감지할 신호의 목록을 가지고 있는 리스트로서, 이 Sensitivity List 객체 중 하나라도 그 값이 변화되면 process문이 수행되는 것이다. 이 때 process문은 첫 문장부터 process내의 마지막 문장까지 코딩상의 순서대로 한 번만 수행한 후 다시 처음으로 돌아가는 형식을 띤다. 이러한 process문 내에서는 일반 프로그래밍 언어에서와 같이 if문, case문, for문 등을 사용할 수 있다.

Process문에 대한 간단한 예제를 살펴보자. 다음 예제에서는 우선 process문 내부의 Sensitivity List로 X. Y, Z, C를 포함하고 있다. 즉 이 4가지 객체의 값 중 하나라도 변경될 경우 이 process문이 수행됨을 의미한다. 이 때 process문의 특징에 따라 beginend 사이를 순서대로 수행한다.

process(X,Y,Z,C) -- X,Y,Z,C를 Sensitivity List로 사용

begin

C <= X; -- being과 end 사이를 순차 실행

A <= X+C;

A <= Y;

B <= X+C;

end process; -- end까지 수행하면 다시 첫 라인으로

경우에 따라서는 Senstivity List가 없는 process문도 존재할 수 있다. 이 경우는 다음의 예제에서처럼 process문의 동작을 정지시키기 위해 하나 이상의 wait 문장을 포함하고 있어야 한다. 그 밖에 process문은 반드시 아키텍처 내부에서만 존재해야 한다는 제약이 있다. 또한 하나의 아키텍처 내부에서도 여러 개의 process문이 존재할 수 있다. 보통 process문을 한 개만 사용할 경우는 process의 이름을 생략해도 상관없다. 하지만 여러 개의 process문을 사용할 경우에는 이들 process문을 상호 구별하기 위해 process문에 이름을 써 주는 것이 좋다.

architecture arch_name of entity_name is

begin

process_name : process -- 프로세서의 이름

선언문

begin

순차 처리문

wait until(조건); -- wait 문장

순차 처리문

.

.

.

wait for(시간) -- wait 문장의 또 다른 형태

.

.

.

end process;

end;

절차적·기능적·데이터 흐름적 모델링

VHDL에서 특정 모듈에 대한 동작의 표현은 크게 절차적 표현과 기능적 표현, 그리고 데이터 흐름적 표현으로 구분될 수 있다. 우선 절차적 표현은 C 프로그램에서처럼 설계하고자 하는 디지털 회로를 하드웨어의 구조와는 직접적인 관계가 없이 단순히 시스템의 동작을 알고리즘 레벨에서 나타낸 것을 말한다. 이러한 절차적 표현은 일반적으로 앞서 설명한 process문 내에서 주로 사용되며 가장 높은 수준의 추상적 설계를 가능케 한다. 즉 일반 수학적 알고리즘을 사용해 프로그래밍이 가능한 모델링 기법이다. 기능적인 모델링은 계층적 설계에서 유용하게 사용되는 방식으로 하위 모듈을 호출하기도 하고, 로직 게이트를 직접 표현하기도 한다. 3가지 모델링 기법 중 가장 하드웨어와 가까운 모델링 기법이라 할 수 있다. 즉 게이트, 버스 등을 비롯한 각각의 하드웨어 컴포넌트들 간의 직접적인 연결을 프로그래밍을 통해 수행한다.

끝으로 데이터 흐름적 모델링 기법이 있다. 이는 절차적 방식과 기능적 방식의 중간 단계 정도에 해당하는 모델링 방법으로서 자료의 흐름을 나타내듯이 시스템의 기능을 나타낸다. 말 자체가 의미하는 바와 같이 신호 및 자료의 제어 흐름의 표현에 초점을 맞추는 설계방식이다. 주로 연산자나 함수 등을 사용해 표현되며, 병행 신호 할당문에 의해 기술된다.

이상의 설명을 바탕으로 또 하나의 예제를 통해 이들 모델링 기법간의 상호 차이에 대해 알아보자.

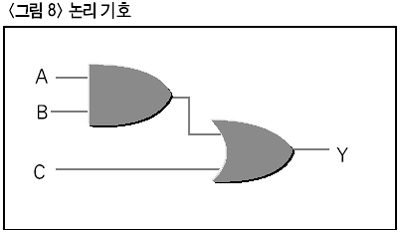

예를 들어 <그림 8>과 같은 회로가 있다고 하자. A, B, C의 3가지 입력과 Y의 출력을 가지며, 간단하게 논리적 and와 or 연산을 수행하는 회로이다. 그리고 이에 대한 진리표가 <표 4>에 나타나 있다. 이를 가지고 지금까지 설명한 각각의 모델링 기법을 사용해 구현해 보도록 한다.

<표 4> 논리 회로의 진리표

|

A

|

B

|

C

|

Y

|

|

0

|

0

|

0

|

0

|

|

0

|

0

|

1

|

1

|

|

0

|

1

|

0

|

0

|

|

0

|

1

|

1

|

1

|

|

1

|

0

|

0

|

0

|

|

1

|

0

|

1

|

1

|

|

1

|

1

|

0

|

1

|

|

1

|

1

|

1

|

1

|

-- 절차적 모델링 기법을 이용한 구현

library ieee;

use ieee.std_logic_1164.all;

entity AND_OR is -- entity 선언 부분

port (A,B,C : in bit;

Y : out bit);

end AND_OR;

architecture behavioral of AND_OR is -- architecture 부분

begin

process(A,B,C)

begin

if C='1'or (A = '1'and B = '1') then Y <= '1';

else Y <= '0';

end if

end process;

end behavioral;

먼저 절차적 모델링 기법이다. 이 예제에서는 절차적 명세를 위해 아키텍처의 process문 내부에 원하는 회로의 동작을 기술했다. process문의 begin과 end 사이의 문장들을 차례대로 수행하면서 Senstivity List A, B, C에 변화가 있을 때마다 이를 수행하는 형식이다. 이 때 주의해야 할 것은 프로그래밍에서 보이는 'and'나 'or'는 논리적 의미의 연산자라는 사실을 기억해야 한다.

-- 기능적 모델링 기법을 이용한 구현

library ieee;

use ieee.std_logic_1164.all;

entity AND is

port(A,B : in std_logic; Y : out std_logic);

end AND;

architecture B_AND of AND is

begin Y <= A and B;

end B_AND;

-----------------------------------------------------

library ieee;

use ieee.std_logic_1164.all;

entity OR is

port(A,B : in std_logic; Y : out std_logic);

end OR;

architecture B_OR of OR is

begin Y <= A or B;

end B_OR;

-----------------------------------------------------

library ieee;

use ieee.std_logic_1164.all;

entity AND_OR is

port(A,B,C : in std_logic; Y : out std_logic);

end AND_OR;

architecture structural of AND_OR is

signal temp : bit;

component AND

port(A,B : in bit; Y : out bit);

end component;

component OR

port(A,B : in bit, Y : out bit);

end component;

begin

ANDgate : AND port map(A,B, temp);

ORgate : OR port map(temp, C, Y);

end structural;

기능적 모델링 기법을 이용한 구현 방법이다. 코드에서 보기에 이 방법은 초기에 AND와 OR에 해당하는 컴포넌트 선언과 이에 대한 사례화(instantiation) 부분이 필요하므로 코드 자체가 조금 길어진 경향이 있지만, 코드에서 제일 아랫 부분의 아키텍처 몸체를 비교하며 살펴보기 바란다. 논리적 and와 or의 동작을 가능케 하는 AND와 OR라는 게이트를 직접 이용해 이에 대한 포트 맵을 통한 회로를 구현한 것이다.

-- 데이터 흐름적 모델링 기법을 이용한 구현

library ieee;

use ieee.std_logic_1164.all;

entity AND_OR is -- entity 선언 부분

port (A,B,C : in bit;

Y : out bit);

end AND_OR;

architecture dataflow of AND_OR is -- architecture 부분

begin

Y <= (A and B) or C;

end dataflow;

끝으로 데이터 흐름적 모델링 기법을 살펴보자. 절차적 모델링 기법과 유사하지만 A, B, C의 데이터 자료의 흐름에 중점을 두어 표현했다는 것을 알 수 있다. 앞서 말한 바와 같이 이 기법은 실제 게이트 맵핑을 통한 기능적 방법과 다분히 알고리즘적인 절차적 방법의 중간 형태의 모델링이라는 것을 알 수 있을 것이다.

예제를 기대하며

지금까지 2회에 걸쳐서‘하드웨어 기술 언어를 이용한 디지털 시스템 설계’를 생각했다. 실제로 디지털 시스템 설계라는 방대한 주제로 한정된 지면에서 2회 정도의 분량으로 완전한 이해를 기대하는 것은 무리다. 하지만 이 글을 통해 디지털 시스템을 설계하는 다양한 방법을 소개했으며, 특히 다양한 설계 방법 중에서 하드웨어 기술 언어를 이용한 설계 방식에 초점을 맞춰 설명했다. 그리고 이러한 하드웨어 기술 언어의 대표적인 예라고 할 수 있는 VHDL을 살펴봤다. 이제 마지막 연재에서는 지금까지 알아본 설계 방법과 VHDL에 대한 이해를 바탕으로 실제 응용을 통한 예제를 다룰 것이다. mas o

정리 : 위윤희 iwish@sbmedia.co.kr

참고자료

- 'HDL Chip Design' A Practical Guide for Designing, Synthesizing and Simulating ASICs and FPGAs using VHDL or Verilog, Douglas J. Smith, Doone Publications

- Xilinx Foundation을 이용한 디지털 시스템 설계, 이준성 외, 복두 출판사

- VHDL을 이용한 CPLD/FPGA 설계, 차영배 편저, 다다미디어

- 디지털 회로 기술 언어 입문, 논리설계와 HDL의 기초, 정희성 외, 홍릉 과학 출판사

- 주문형 반도체 설계 ASIC DESIGN, 최명렬, 하이테크정보

|

박스기사

예약어와 키워드

요즘 예약어(reserved word)와 키워드(keyword)가 주로 같은 의미로 사용되는 경우가 많다. 그리고 사실 이것이 틀린 말은 아니다. 하지만 엄밀한 의미에서 보면 이 두 용어 사이에는 분명한 차이가 있다. 예약어는 프로그래밍을 할 때에 미리 그 '사용처'가 정해져 있어 이를 식별어로서 사용할 수 없음을 나타낸다. 이에 반해 키워드는 해당 언어에서 그 '의미'가 미리 정해져 있는 문자열을 뜻한다. 즉 키워드의 경우 의미만 지정되어 있을 뿐이지 그 사용처가 미리 정해져 있다는 말은 아니다. 따라서 키워드는 식별어로서 사용할 수 있다. 예를 들면 'if'라는 것이 예약어가 아닌 키워드로 사용될 경우 변수의 이름으로도 사용될 수 있음을 의미한다. 하지만 상식적으로 생각해 볼 때 키워드를 예약어로 인정하지 않을 경우 프로그래밍의 가독성을 떨어뜨려 상당히 읽기 난해한 코드 형태가 될 것이다. 따라서 요즈음 대부분의 프로그래밍 언어들은 이러한 키워드를 예약어로서 사용하기 때문에 정의 상 이들 사이에는 차이기 있긴 하나 오늘날 두 용어를 거의 같은 의미로 사용하고 있다.

|

|

![]()