Guide for Leonardo Spectrum Synthesis tool

Invoking the Leonardo Environment

- Invoke Leonardo with the following command: [>leo &].

- Select LeonardoSpectrum Level 3 and press OK;

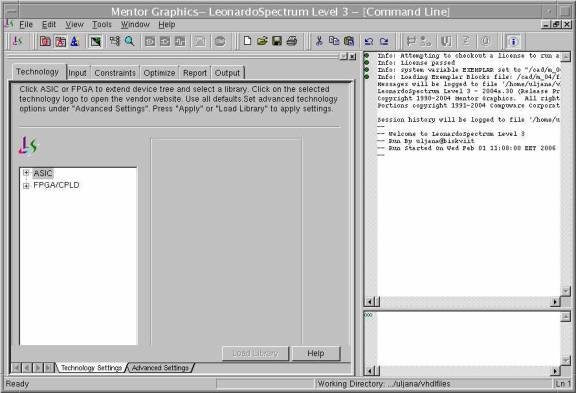

- The following window will appear to you (Figure 1);

Figure 1 First window opening with Leonardo Spectrum synthesis tool

The basic steps required to synthesize a HDL design are the following:

- Selecting a target technology for synthesis;

- Reading in the HDL design;

- Synthesizing the design (optimizing the logic and mapping to the target technology);

- Writing out the synthesized netlist in a format, which can be used by gate-level simulation and/or FPGA layout tools.

To follow all these steps select Advanced FlowTabs by icon with red A letter. Tabs depict basic steps.

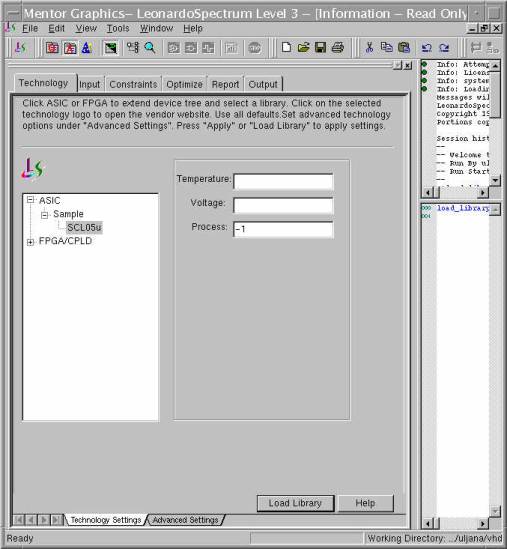

Selecting target technology

- Select tab Technology;

- Open list under the ASIC directory;

- Open list under the Sample directory;

- Choose SCS05u technology

- Press Load Library button.

Figure 2 Technology selection window

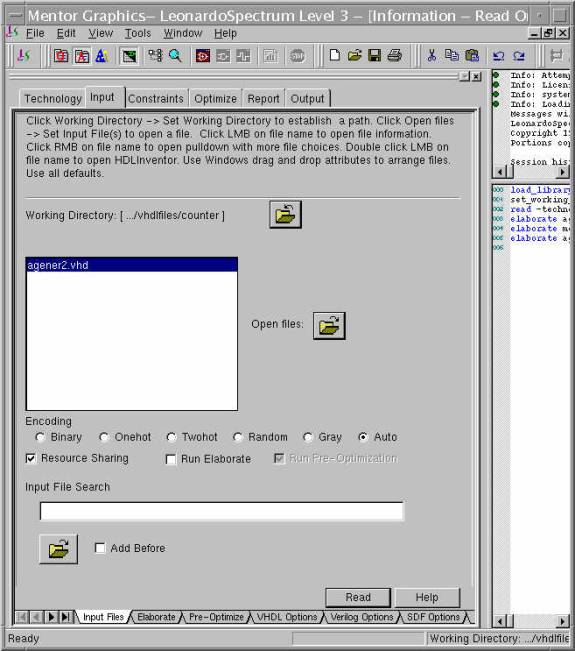

Reading the input design

- Select tab Input;

- Specify working directory - the directory where you want to create working files for Leonardo;

- Open files you want to synthesize with a specific button (for example counter.vhd);

- Select the file you want to read now in the window with opened files;

- Take off the tick in Run Elaborate option;

- Press Read button;

Figure 3 Reading design window

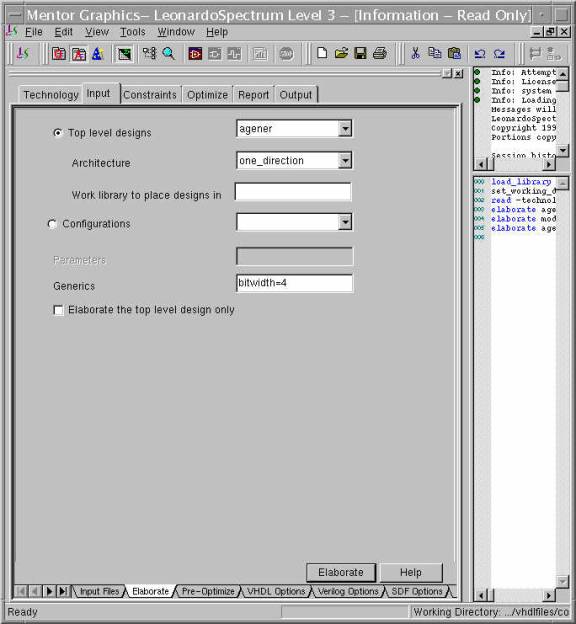

- Select Elaborate tab (these tabs are down);

- Specify top level design, for example agener and corresponding architecture (in our example one_direction);

- Into the field Generics specify generic values, for example bitwidth=4;

- Press Elaborate button;

Figure 4 Elaborate Design window

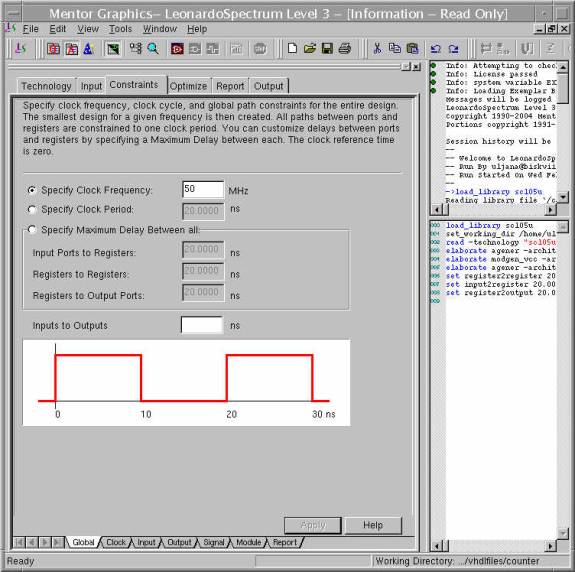

Specifying constraints

- Select tab Constraints;

- Specify clock frequency;

- Press Apply button;

Figure 5 Specifying constraints window

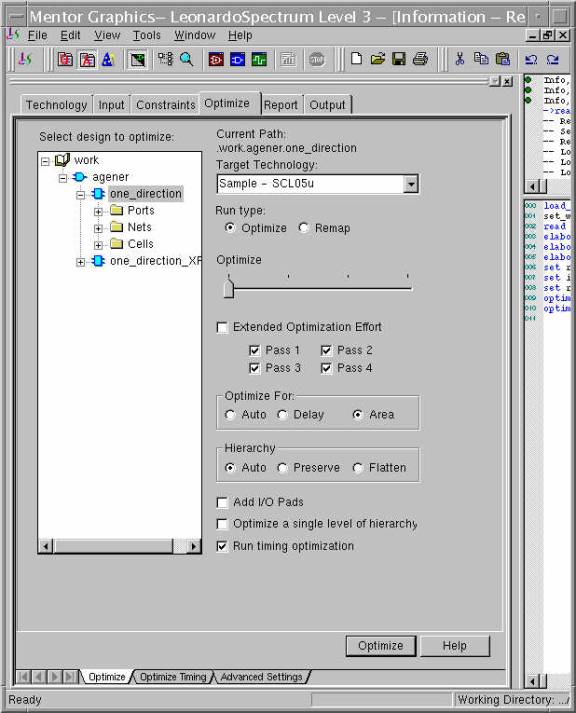

Synthesizing the design

- Select tab Optimize;

- Press Optimize button;

Figure 6 Optimize window

Navigation in the hierarchy

- Find “View RTL Schematic” icon to see the RTL schematic view of the

- synthesized design;

- Find “View Technology Schematic” icon to see technology schematic view of the synthesized design;

Generating Reports

- Select tab Report;

- Down tabs specify report types: Report Area and Report Delay;

- You can either specify the report to the file or just to see it in the command window (in the lab’s report these results should be added).

Exiting the synthesis tool

- File => Exit